|

|

|

|---|

Titlul proiectului: ”Tehnologie pentru circuite integrate cu nod electronic de 2 nm”

Acronim: IT2

Tipul proiectului: Proiect European H2020

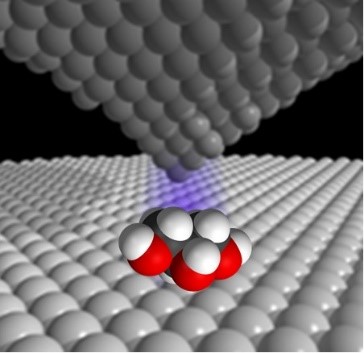

Proiectul IT2 vizează crearea unor descoperiri ale tehnologiei cheie pentru a duce Roadmap-ul Semiconductorilor la nodul de 2 nm.

Obiectivul general al proiectului IT2 este explorarea, descoperirea, dezvoltarea și demonstrarea opțiunilor tehnologice necesare pentru realizarea tehnologiei logice CMOS de 2nm. Aceste activități sunt: Litografie, Explorare de Procese și Module și Metrologie.

Obiectivul cheie legat de partea dedicată Explorării Procesului și Modulului este evaluarea soluțiilor tehnologice existente și inovatoare, care permit industriei să țină pasul cu legea de scalare a lui Moore și să îndeplinească specificațiile de performanță, putere, suprafață și cost (PPAC) pentru nodul de 2nm.

Obiectivul principal pentru activitățile de Metrologie este de a dezvolta în continuare capacitățile metrologice, de caracterizare și inspecție, având sensibilitate și precizie suficiente pentru a studia etapele procesului nodului de 2nm și pentru a stabili corelații între parametri și rezultatele procesului la nivelul plachetei pentru nodul de 2nm. Mai mult, metrologia care trebuie dezvoltată trebuie să fie suficient de rapidă pentru a genera date relevante statistic, necesare pentru a cuantifica stochastica proceselor și interdependențele existente în proiectarea proceselor.

Principalul subiect abordat în proiectul IT2 vizează capitolul 10 denumit „Proces Tehnologic, Echipamente, Materiale și Fabricare pentru Componente și Sisteme Electronice” din ECSEL MASP 2019, cu accent pe provocarea majoră 4, și anume „Extinderea leadership-ului mondial în Echipamente pentru Industria Semiconductorilor, soluții privind Materialele și Fabricarea blocurilor avansate de semiconductori, pentru ambele tehnologii „More-Moore”. și „More-than-Moore” pentru ambele „Sistem pe Chip (Sytem on Chip)” și pentru „Sistem Încapsulat (System in Package)” eterogene, provocarea majoră 1 „Dezvoltarea tehnologiei avansate de logică și memorie pentru integrare la nivel nanometric și performanța bazată pe aplicații” și provocarea majoră 2 „Dezvoltarea Tehnologiei pentru integrare eterogenă a Sistem pe Chip (System on Chip – SoC)”.